Digital Frontend

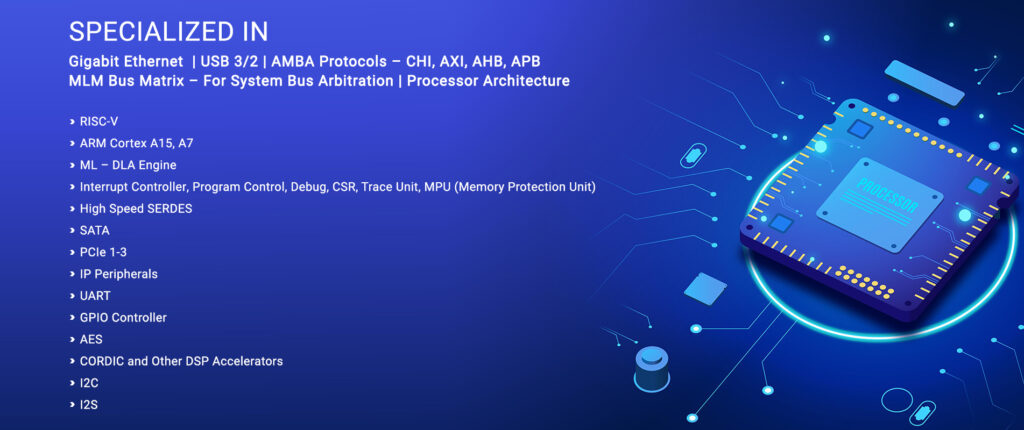

We have a strong team of experts in Microarchitecture, RTL Design, IP & SoC Verification, and GLS

We have successfully delivered projects on 5G ORAN Radio Unit, Ethernet Phy, RISC V Processor, Battery Management System, NVME SSD Controllers and Memory Controllers

The team has vast experience in Designing and Verifying Automotive SoCs, Microprocessors, Consumer Electronics SoCs, EV SoCs, and PCI buses

Digital Design & Architecture

- Micro-Architecture

- RTL Design

- RTL QC check : Lint, CDC & more

- SoC/Subsystem Integration

- Low Power Design Implementation

- UPF, CLP

- Timing Constraints, Synthesis, STA, LEC

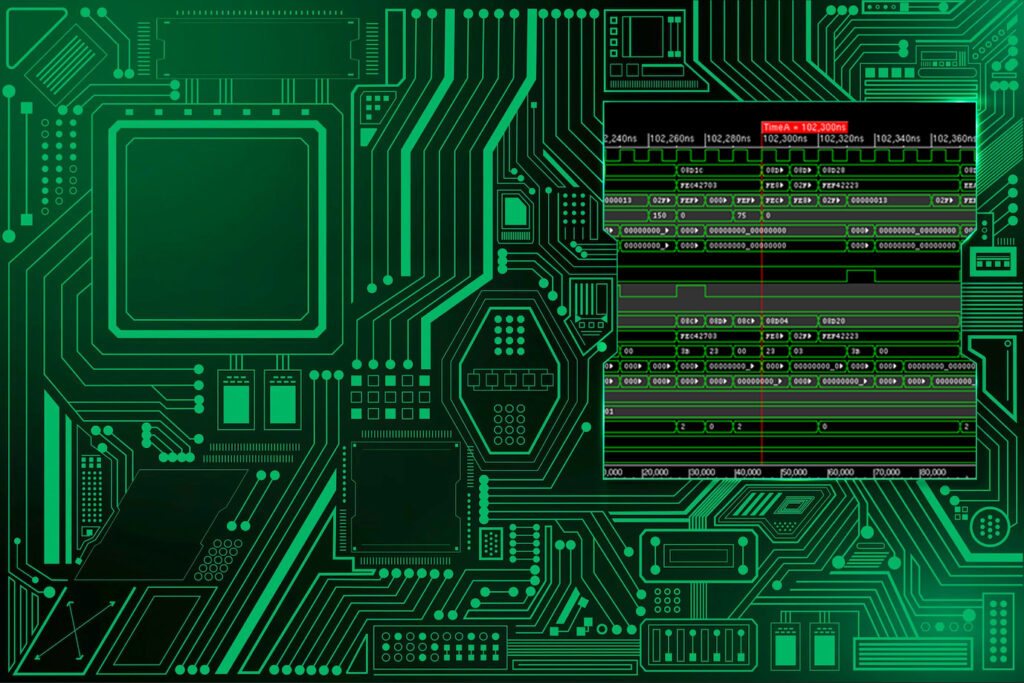

Digital Verification

- Advanced IP & SoC Verification

- SV-UVM based Constraint – Random Verification

- Test Plan, Test Bench Development, Development of BFMs, Monitors, Assertions, Checkers, Debug Automation

- Low Power Verification (CPF/UPF flows)

- Gate Level Simulations – Test Bench BringUp (Identification of Sync Flops, Prioritisation of TestCases, Identification of Various CDC Paths, Resolution / Upgradation of Test Failures Due to X Propagation)

- PCIe, Ethernet, AMBA Protocols, RISC-V, DSP, Crypto processor – IP and Functional Verification in SoC environment

- Coverage – Toggle, Code, Functional

- Formal Verification

- VIP Development and Integration

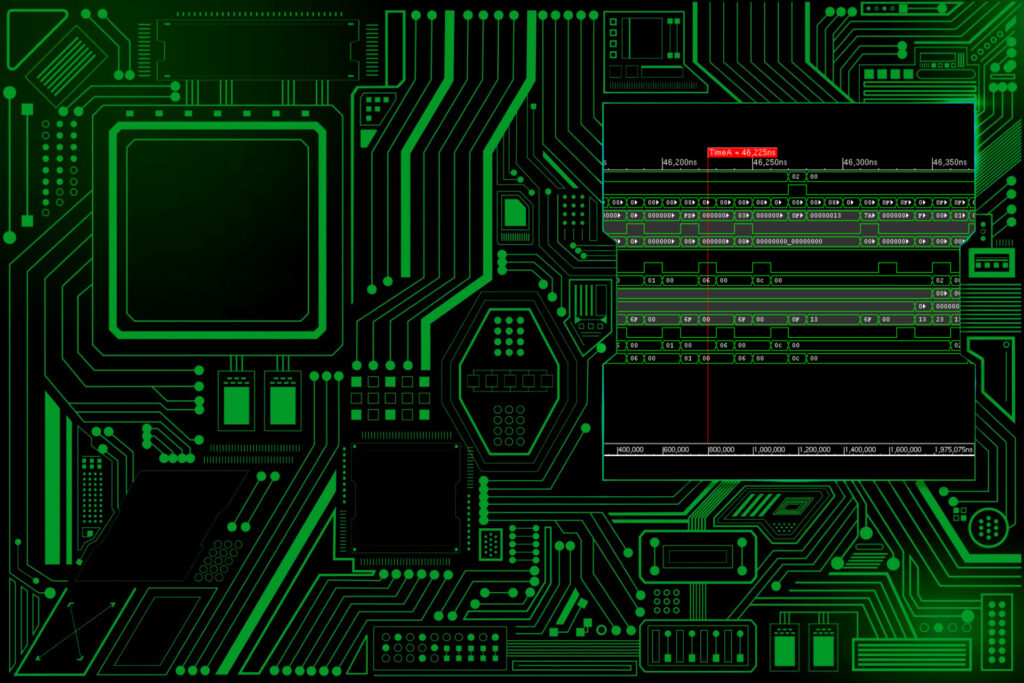

Post Validation Support

- Post Silicon Validation – ATP and Timeset Generation for J750 and Advance Teradyne Testers

- EVCD Generation for Characterization

- Die Yield Analysis on Wafersort

- Parameterisation Tests – IO Leakage – Analog and Digital TX / RX, Stuck at Patterns, Sequences to detect PVT Corner values for IO Calibration, Regulator Calibrations, DC IO — Measurements (GPIOs, DDR PADs for Impedance and Hysteresis) & more